# PHILIPS

# PRODUCT BOOK

PHILIPS

ELECTRONIC COMPONENTS

# PRINTED CIRCUIT BOARDS

A guide to specifying and designing

# **Printed Circuit Boards**

# **Printed Circuit Boards**

A guide to specifying and designing

edited by C. Thomas Publications Dept. Eindhoven

PUBLICATIONS DEPARTMENT ELECTRONIC COMPONENTS AND MATERIALS DIVISION © N.V. Philips' Gloeilampenfabrieken EINDHOVEN - The Netherlands October 1971

The publication of this document does not imply a licence under any patent

# Contents

| 1 | Gene | eral                                                       |

|---|------|------------------------------------------------------------|

|   | 1.1  | Introduction                                               |

|   | 1.2  | Definitions                                                |

|   | 1.3  | Classification of PCB types                                |

|   | 1.4  | Producing the conductor pattern                            |

|   |      | 1.4.1 Subtractive process                                  |

|   |      | 1.4.2 Additive process                                     |

|   | 1.5  | Resist application methods                                 |

|   |      | 1.5.1 Screen resist                                        |

|   |      | 1.5.2 Photopolymer film resist                             |

|   |      | 1.5.3 Photo resist                                         |

|   |      | 1.5.4 Reversed etch method                                 |

|   |      | 1.5.5 Direct method                                        |

| 2 | Base | 9 Materials                                                |

| 2 | 2.1  | Classification                                             |

|   | 2.1  | 2.1.1 Paper base laminates                                 |

|   |      | 2.1.2 Glass base laminates                                 |

|   | 2.2  | Essential properties                                       |

|   |      | 2.2.1 Comparison of types                                  |

|   |      | 2.2.2 Surface and volume resistance                        |

|   |      | 2.2.3 Max. operating temperature                           |

|   |      | 2.2.4 Flatness limits                                      |

|   | 2.3  | Material specifications and U.Lapproval                    |

|   |      | 2.3.1 Base materials                                       |

|   |      | 2.3.2 Base material identification                         |

|   |      | 2.3.3 U.Lapproval                                          |

| 3 | Boa  | rd Fabrication                                             |

| 5 | 3.1  | Board contour and its location w.r.t. holes and pattern 15 |

|   |      | 3.1.1 Contouring by sawing with a sawing jig               |

|   |      | 3.1.2 Contouring by milling                                |

|   |      | 3.1.3 Contouring by sawing without a sawing jig            |

|   |      | 3.1.4 Contouring by punching                               |

|   |      | 3.1.5 Making cut-outs by milling to a stop                 |

|   |      | 3.1.6 Milling cut-outs by means of a milling jig           |

|   | 3.2  | Hole size                                                  |

|   |      | 3.2.1 Plated-through holes                                 |

|   |      | 3.2.2 Non-plated holes                                     |

| 3.3  |         | ance on hole spacing                                    |     |    |

|------|---------|---------------------------------------------------------|-----|----|

|      |         | Plated-through holes                                    |     |    |

|      |         | Non-plated holes                                        |     |    |

| 3.4  |         | nsional changes caused by shrinkage and/or expansion of |     |    |

|      |         | material                                                |     |    |

|      | 3.4.1   | Permanent dimensional change caused by the PCB fa       |     |    |

|      | 5 S S L | process                                                 |     |    |

|      | 3.4.2   | Dimensional change in the finished board due to temper  |     |    |

| 3.5  |         | ess limits                                              |     |    |

|      | 3.5.1   | Specifying flatness                                     | • • | •  |

| Patt | ern .   |                                                         |     |    |

| 4.1  | Gener   | ral                                                     |     |    |

| 4.2  |         | n classes                                               |     |    |

| 4.3  | Patter  | n tolerances                                            |     |    |

|      | 4.3.1   | Master pattern tolerance                                |     |    |

|      | 4.3.2   | Fabrication tolerance                                   |     |    |

| 4.4  | Misal   | ignment of pattern with respect to holes                |     |    |

| 4.5  | Estab   | lishing artwork dimensions                              |     | ×. |

| 4.6  | Minin   | num pattern configurations                              |     |    |

| 4.7  | Patter  | n configuration                                         |     |    |

|      | 4.7.1   | Conductor path and form                                 |     |    |

|      | 4.7.2   | Distribution of conductor pattern                       |     | ·  |

|      | 4.7.3   | Configuration of current distribution aids              |     |    |

|      | 4.7.4   | Influence of pattern on solderability of holes          |     |    |

|      | 4.7.5   | Identification marks                                    |     |    |

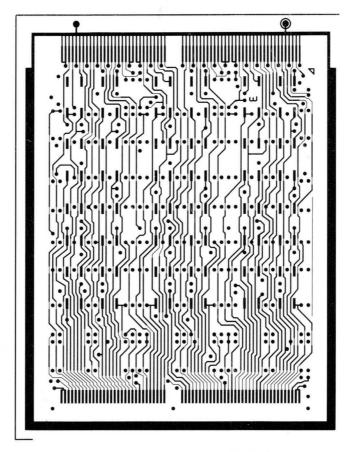

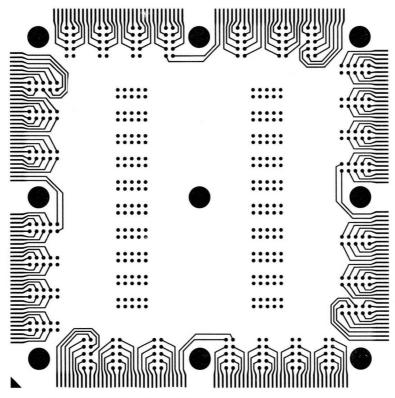

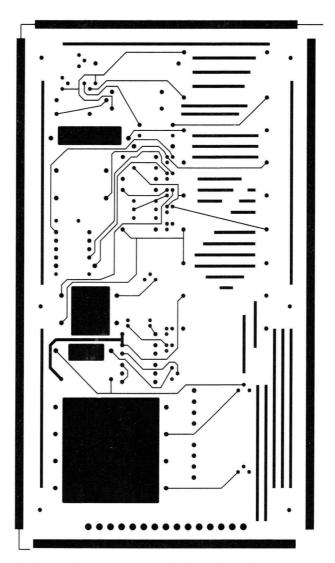

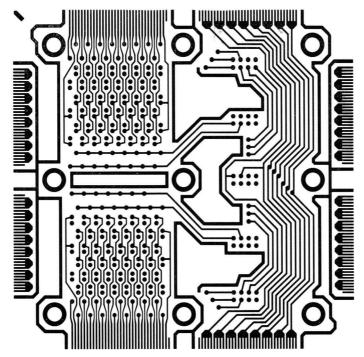

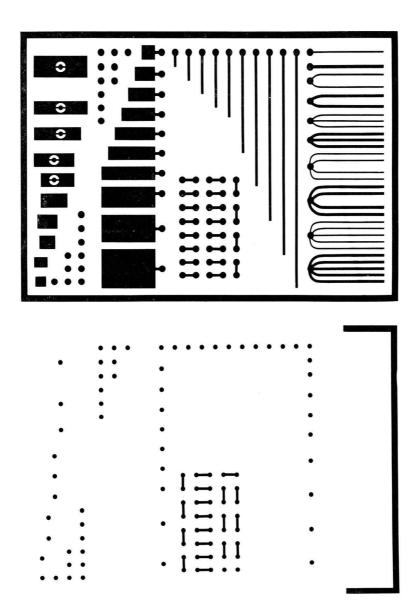

|      | 4.7.6   | Example patterns                                        |     |    |

|      | 4.7.7   | Contacts for edge-connectors                            |     |    |

| 4.8  | Under   | rcut and overhang                                       |     |    |

|      | 4.8.1   | Definitions                                             |     |    |

|      | 4.8.2   | Measurement                                             |     | ·  |

| Plat | ed-Thro | ough Holes                                              |     |    |

| 5.1  | Funct   | ion of plated-through hole                              |     |    |

|      | 5.1.1   | Improved component attachment                           |     |    |

|      | 5.1.2   | Electrical interfacial connection                       |     |    |

| 5.2  | Use of  | f plated-through holes                                  |     | ÷. |

|      | 5.2.1   | In single-sided PCB's                                   |     |    |

|      | 5.2.2   | In double-sided PCB's                                   |     |    |

|   | 5.3  | Inspect   | ion of plated-through holes                                   | 51 |

|---|------|-----------|---------------------------------------------------------------|----|

|   |      | 5.3.1     | Solderability test                                            | 51 |

|   |      | 5.3.2     | Re-soldering test                                             | 51 |

|   |      | 5.3.3     | Continuity                                                    | 52 |

|   | 5.4  | Mounti    | ng recommendations                                            | 53 |

| 6 | Coa  | tings and | After-Treatments                                              | 56 |

|   | 6.1  | Introdu   | letion                                                        | 56 |

|   | 6.2  |           | -plating                                                      | 56 |

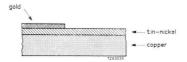

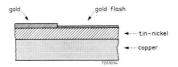

|   |      |           | Approved plating metals                                       | 56 |

|   |      | 6.2.2     | Other commonly used plating metals                            | 58 |

|   | 6.3  | Plating   | other than by electro-deposition                              | 60 |

|   |      | 6.3.1     | Approved method                                               | 60 |

|   |      | 6.3.2     | Other commonly used methods                                   | 60 |

|   | 6.4  | After-ti  | reatment of metallic coatings                                 | 61 |

|   |      | 6.4.1     | Re-flow                                                       | 61 |

|   |      | 6.4.2     | Hydrosqueegee                                                 | 61 |

|   | 6.5  | Organi    | c coatings                                                    | 62 |

|   |      | 6.5.1     | Temporary protective coating on copper                        | 62 |

|   |      | 6.5.2     | Permanent protective coating, insulating coating or solder    |    |

|   |      |           | resist on copper and tin-lead                                 | 62 |

| 7 | Sold | erability |                                                               | 64 |

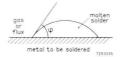

|   | 7.1  | Terms     | and definitions                                               | 64 |

|   | 7.2  | Soldera   | bility of metal finishes on PCB's                             | 65 |

|   |      | 7.2.1     | Tin-lead                                                      | 65 |

|   |      | 7.2.2     | Copper                                                        | 67 |

|   |      | 7.2.3     | Gold                                                          | 67 |

|   |      |           | Tin                                                           | 67 |

|   |      |           | Nickel                                                        | 68 |

|   |      |           | Tin-nickel                                                    | 68 |

|   |      |           | Tin-nickel with a thin gold layer                             | 68 |

| 8 | Con  | ductor W  | idth and Conductor Spacing related to Electrical Requirements | 69 |

|   | 8.1  | Condu     | ctor width                                                    | 69 |

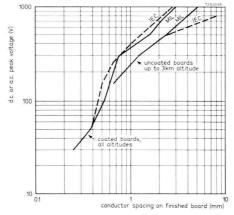

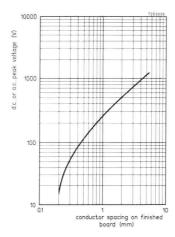

|   | 8.2  | Condu     | ctor spacing                                                  | 69 |

|   |      | 8.2.1     | General                                                       | 69 |

|   |      | 8.2.2     | Calculation of minimum conductor spacing                      | 70 |

|   |      | 8.2.3     | Explanatory notes on the graphs Figs 8.2 and 8.3              | 72 |

| Test | s, Operating conditions, Delivery and Test Boards                              |

|------|--------------------------------------------------------------------------------|

| 9.1  | Tests and operating conditions                                                 |

| 9.2  | Delivery                                                                       |

|      | 9.2.1 Complaints procedure                                                     |

|      | 9.2.2 Sample size and inspection level                                         |

|      | 9.2.3 Fault classification                                                     |

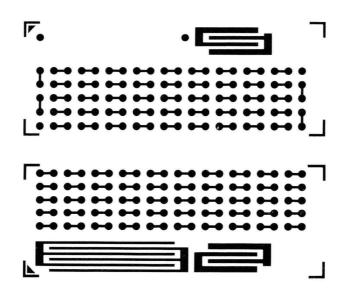

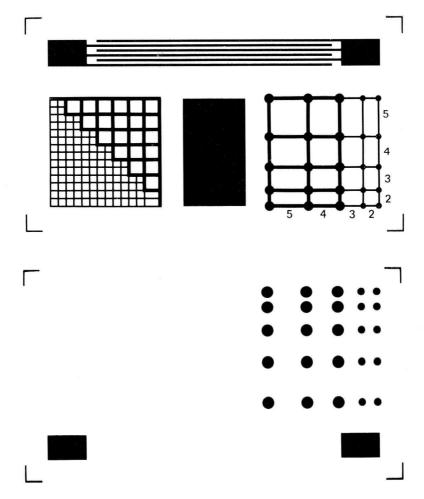

| 9.3  | Test boards                                                                    |

|      | 9.3.1 Test board to check solderability                                        |

|      | 9.3.2 Test board to check hole quality                                         |

|      | 9.3.3 Test board to check the insulation resistance 84                         |

|      | 9.3.4 Test board to check peel strength                                        |

|      | 9.3.5 Test board to check electrical properties                                |

|      | 9.3.6 Test board to check organic coatings                                     |

| 9.4  | UL-approval                                                                    |

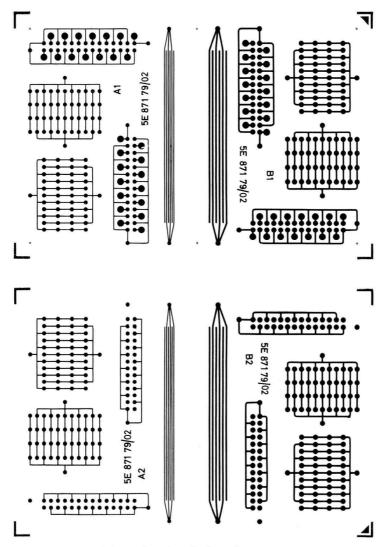

| Mas  | ter Pattern and Master Drawing                                                 |

|      | Master pattern                                                                 |

|      | 10.1.1 Materials                                                               |

|      | 10.1.2 Definitions                                                             |

|      | 10.1.3 Types of master patterns and their dimensions 95                        |

|      | 10.1.4 Quality and tolerances                                                  |

| 10.2 | Engineering detail drawing (master drawing)                                    |

|      | 10.2.1 Function                                                                |

|      | 10.2.2 Lay-out                                                                 |

|      | 10.2.3 Dimensioning                                                            |

|      | <ul><li>9.1</li><li>9.2</li><li>9.3</li><li>9.4</li><li>Mas<br/>10.1</li></ul> |

#### Appendix

| A.1 | Gen  | eral                            | • | ł | ÷ | • | · | · | • | · | · | ŀ | · | • | ÷ | · | • | • | 2 | · | 105 |

|-----|------|---------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| A.2 | Clas | ssification and test conditions |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 105 |

|     | 2.1  | Classification                  |   |   | ÷ |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   | 105 |

|     | 2.2  | Standards of acceptance         |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 108 |

|     | 2.3  | Applicable documents .          |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 108 |

|     | 2.4  | Order of precedence             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 108 |

|     |      | Photo master ,                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |

| A.3 | Requirements to be satisfied by base materials                        |

|-----|-----------------------------------------------------------------------|

| A.4 | Visual requirements for PCB's                                         |

|     | 4.1 Comparison with standard                                          |

|     | 4.2 General requirements                                              |

|     | 4.3 Electroplating                                                    |

|     | 4.4 Undercut                                                          |

|     | 4.5 Plated through holes                                              |

| A.5 | Dimensional requirements                                              |

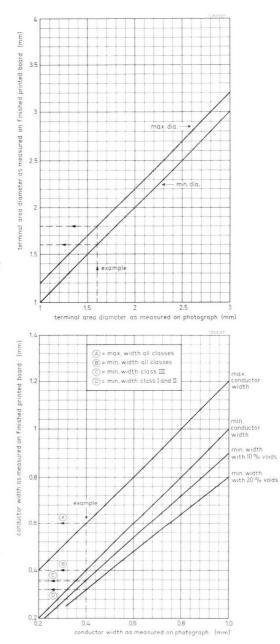

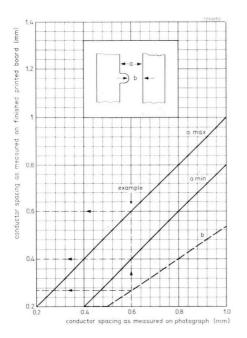

|     | 5.1 Conductor pattern dimensions                                      |

|     | 5.2 PCB dimensions                                                    |

| A.6 | Requirements to be satisfied by electroplating                        |

|     | 6.1 Plating material and thickness                                    |

|     | 6.2 Plating thickness measurement                                     |

|     | 6.3 Plating adhesion                                                  |

| A.7 | Solderability requirements                                            |

|     | 7.1 PCB surface                                                       |

|     | 7.2 Plated-through holes                                              |

|     | 7.3 Solderability test                                                |

|     | 7.4 Solderability after storage                                       |

| A.8 | Electrical requirements                                               |

|     | 8.1 Insulation resistance                                             |

|     | 8.2 Dielectric strength                                               |

| A.9 | Requirements on plated-through holes                                  |

|     | 9.1 Re-soldering                                                      |

|     | 9.2 Continuity of interfacial connection by plated-through hole after |

|     | soldering                                                             |

|     | 9.3 Reliability of interfacial connection by plated-through hole 122  |

# Acknowledgement

Acknowledgement is made to W. van der Zwaal of the Development Laboratory, Eindhoven, who supplied the information on which this book is based.

## Foreword

This book is primarily intended as a working handbook to assist intending customers to produce their own designs for Printed Circuit Boards and, at the same time, make the most advantageous use of our production capability. It includes details on the selection of materials, processes and finishes and provides a standardised approach to specifying. This should help to obviate some of the fabrication difficulties which frequently have an unfavourable effect on the price and delivery of PCB's.

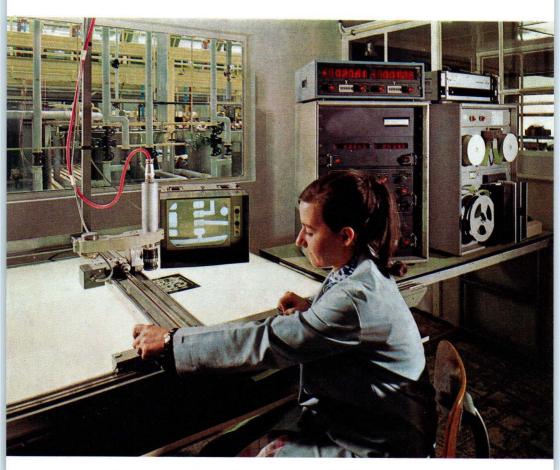

A second objective is to provide some insight into the scale and potential of our PCB manufacturing facility and also to indicate levels of quality and reliability which can be obtained when the right approach is made at the outset.

To-day's largest volume requirement for PCB's is for rigid double-sided boards with finely detailed wiring patterns and it is these which are discussed in this book. It is our experience that specifications for PCB's of this type are not always representative of the actual requirement and that they are frequently expressed in a manner which can be misinterpreted. Surprising though it may seem in these days of value engineering, where every component is subject to scrutiny, PCB's with, for example, inappropriate and costly platings and unnecessarily close tolerances, are regularly asked for. Precious metal finishes are often added purely for appearance since this is an important influence on the acceptability of high value products; but care must be exercised to make sure that eye-appeal is not at the expense of other properties. For instance, it may not be generally realised that gold diffusion can cause embrittlement of solder joints and that it is of small value as a protective finish unless a carefully controlled, impervious layer is deposited.

A supplier might sometimes feel inclined to advise his customer that a more economic and appropriate design is possible; but, at a stage where all the drawings and documentation have been raised, such advice is unlikely to be received with enthusiasm. It is to preclude the need for such advice that this book has been prepared.

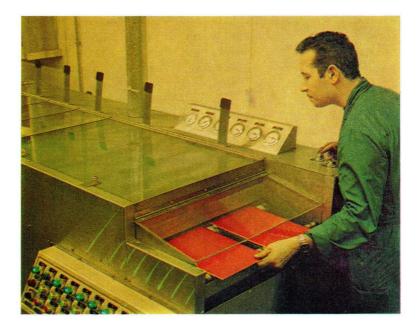

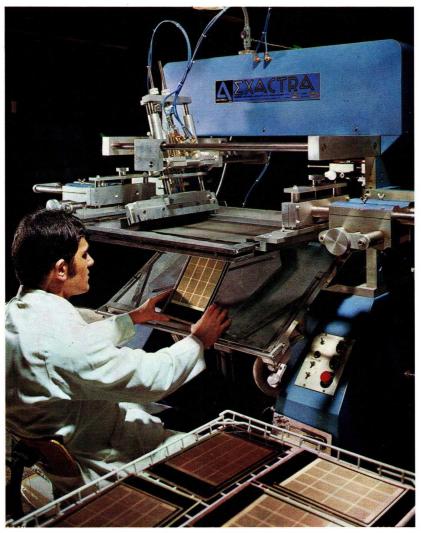

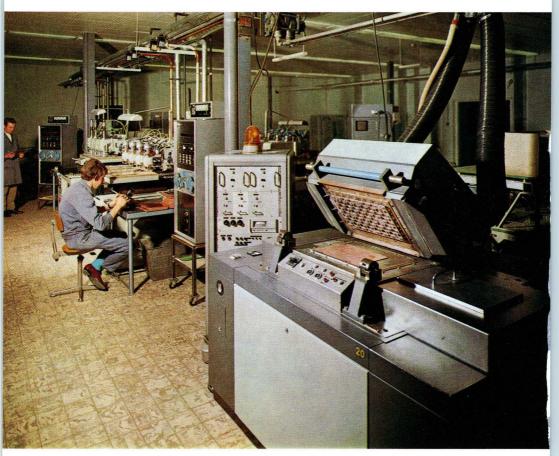

Dry film processor

## 1 General

#### **1.1 Introduction**

Detailed recommendations follow for the design of rigid single and double-sided printed circuit boards, with or without plated-through holes and with or without edge-connectors. These recommendations are in accordance with the General Specification which appears as an Appendix at the rear of the book. Table 1.1 summarizes the main design considerations and cross-refers to later sub-sections where the various points are dealt with.

#### **1.2 Definitions**

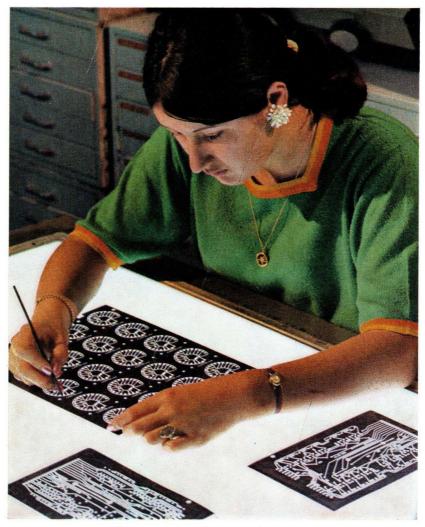

*Artwork* – an accurately scaled representation of the conductor pattern layout which is used to produce the master pattern.

*Master drawing* – a drawing showing the dimensional limits or grid location applicable to any or all parts of a PCB, including the base.

*Master pattern* (or photo master) -a 1 to 1 scale pattern which is used to produce the conductor pattern within the accuracy specified on the master drawing.

These definitions are in accordance with Specification IPC.D. 310.

#### 1.3 Classification of board types

The types of printed circuit boards discussed in this book are classified in Table 1.2.

#### 1.4 Producing the conductor pattern

#### 1.4.1 SUBTRACTIVE PROCESS

From a base material clad on one or both sides with copper of, usually, 35  $\mu$ m thickness, the excess copper is etched away to leave the desired conductor pattern.

| Table 1.1 Summary of main design considerations | design considerations                                                                                                                                                                                                 |                                                                                                             |                                                                                          |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| design consideration                            | recommendation                                                                                                                                                                                                        | advantage gained                                                                                            | to be achieved by                                                                        |

| length of production run                        | - as large as possible<br>(see sub-section 3.1)                                                                                                                                                                       | <ul> <li>acquisition of special tool justified</li> </ul>                                                   | - standard outer dimensions<br>for different patterns                                    |

| dimensions                                      | <ul><li>as small as possible</li><li>(see sub-section 3.4)</li></ul>                                                                                                                                                  | <ul> <li>less influence by tolerances – adapting the electrical</li> <li>less reject cost design</li> </ul> | - adapting the electrical design                                                         |

| shape                                           | <ul> <li>rectangular</li> <li>without flatness limits<br/>(see sub-sections<br/>3.1 and 3.5)</li> </ul>                                                                                                               | <ul> <li>ease of contour<br/>fabrication</li> <li>reject percentage reduced</li> </ul>                      | - adapting the device where<br>the PCB is to be used                                     |

| base material                                   | <ul> <li>not paper base laminate</li> <li>no specified supplier</li> <li>(see section 2)</li> </ul>                                                                                                                   | <ul> <li>better hole quality</li> <li>base material always</li> <li>available from stock</li> </ul>         | <ul> <li>accepting different makes and<br/>slight difference in colour</li> </ul>        |

| plated-through holes                            | <ul> <li>one hole diameter per<br/>board</li> <li>diameter according to<br/>preferred diameter range</li> <li>same hole pattern for as<br/>many board types as<br/>possible</li> <li>(see sub-section 3.2)</li> </ul> | - cheaper                                                                                                   | <ul> <li>adapting the electrical<br/>design and using suitable<br/>components</li> </ul> |

|                                                 |                                                                                                                                                                                                                       |                                                                                                             |                                                                                          |

Table 1 1

| Tuble 1.1 Communed)                            |                                                                                                                                                                                                                                                                                                                          |                                                                                                              |                                                                                                                    |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| pattern                                        | <ul> <li>avoid fine detail</li> <li>wherever possible</li> <li>even distribution</li> <li>front to back registration</li> <li>as accurate as possible</li> <li>suitable, correctly placed,</li> <li>distribution aids</li> <li>eliminate effect of pattern</li> <li>on solderability</li> <li>(see Section 4)</li> </ul> | <ul> <li>fewer rejects</li> <li>better electro-plating quality</li> <li>better hole solderability</li> </ul> | <ul> <li>adapting the electrical design</li> <li>following recommendations</li> <li>in Section 4</li> </ul>        |

| operating conditions                           | <ul> <li>arrange to be in<br/>accordance with<br/>para A 2.2<br/>(see also sub-section 9.1)</li> </ul>                                                                                                                                                                                                                   | <ul> <li>no need for extra<br/>investigation</li> </ul>                                                      | - adapting the device where<br>the PCB is to be used                                                               |

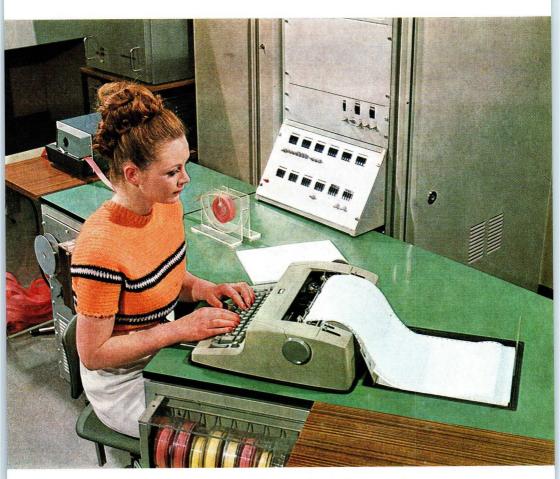

| master pattern<br>(photo master)               | <ul> <li>produce as accurately<br/>as possible</li> <li>arrange front to back<br/>registration as accurately<br/>as possible</li> <li>(see sub-section 10.1)</li> </ul>                                                                                                                                                  | <ul> <li>no delay in delivery<br/>(due to inaccurate master<br/>pattern)</li> </ul>                          | <ul> <li>automated artwork</li> <li>generation</li> <li>use of precision camera</li> </ul>                         |

| master drawing<br>(Engineering detail drawing) | <ul> <li>produced in a clear and<br/>unambiguous form<br/>(see sub-section 10.2)</li> </ul>                                                                                                                                                                                                                              | <ul> <li>no misunderstandings, no delays in production</li> </ul>                                            | <ul> <li>employing a standard<br/>drawing system, preferably<br/>as recommended in<br/>sub-section 10.2</li> </ul> |

|                                                |                                                                                                                                                                                                                                                                                                                          |                                                                                                              |                                                                                                                    |

Table 1.1 (Continued)

| board type plating<br>plated<br>single-and<br>double-sided | plating    | holes     process (see s section 1.2)       section 1.2)     section 1.2)       plated-through     subtractive       non-plated     subtractive       plated-through     subtractive | process (see sub-<br>section 1.2)<br>sentractive<br>semi-additive<br>subtractive<br>semi-additive | mask application (see sub-section 1.3)<br>screen resist, reversed etch<br>photopolymer dry film resist, reversed etch |

|------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|                                                            | non-plated | non-plated                                                                                                                                                                           | subtractive                                                                                       | screen resist, direct<br>photopolymer dry film resist, direct<br>photo resist, direct                                 |

Table 1.2 PCB Classification

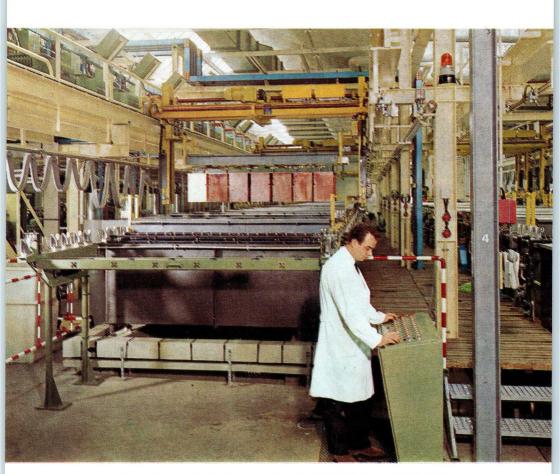

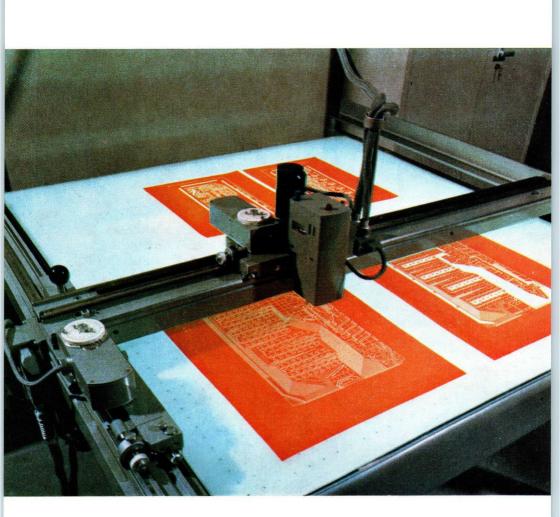

Semi-automatic screen printing machine.

#### 1.4.2 Additive process

Copper is deposited on a dielectric material, by chemical reduction, to produce the desired conductor pattern. Etching is not required.

A variant of this method is the semi-additive process, here a copper layer is deposited on the entire surface of a plain base material by chemical reduction and then built-up to 5  $\mu$ m thickness by electroplating. Thereafter, resist is applied and the copper in the holes and on the conductor pattern is built-up to the desired thickness by a further stage of electroplating. Finally the excess copper is removed by etching. Both the additive and the semi-additive processes are suitable for the production of PCB's with plated-through holes but without etch resistant electroplatings. From a printing point of view, copper-plated boards are preferred. For solderability see para 7.2.2. For organic coatings see subsection 6.5.

#### **1.5 Resist Application Methods**

#### 1.5.1 SCREEN RESIST

Resist is forced through the openings of a tightly stretched screen, usually made of metal, onto the underlying board. The desired conductor pattern can be either the unmasked portion of the screen (see "direct method") para 1.5.5) or the masked portion (see "reversed etch method" para 1.5.4). Screen masking is accomplished photomechanically.

#### **1.5.2 Photopolymer film resist**

This is a dry film resist which forms a light-sensitive film when laminated to the board surface. For the reversed etch method it is exposed to light through a positive. For the direct method it is exposed through a negative of the desired wiring configuration. The light sensitive film is a negative photo-layer, so after development the exposed areas harden and are retained on the board.

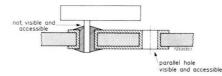

Dry film resist techniques are particularly suitable for boards requiring plated-through holes and patterns too finely detailed for the screenprinting method. In addition, they enable boards with plated-through holes to be made with the conductor pattern and hole plating of bare copper. This is achieved by applying a positive resist on the plated board so that the holes are bridged over. As the dry film is an etch resist, it seals the interiors of the platedthrough holes and protects the walls during etching. This is known as the "tenting-over" technique.

#### 1.5.3 Photo resist

This is a liquid light-sensitive resist which is applied on the board by dipping, and then dried.

In most cases a negative resist is used so that the exposed areas are retained on the board after development. Liquid light sensitive resist is not recommended for boards with plated-through holes.

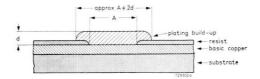

#### 1.5.4 Reversed etch method

With this method a negative, or reverse resist pattern is applied over the unwanted metal. Copper is then electroplated on the walls of the holes and on the exposed conductor pattern. Finally a metal etch resist is applied in these areas. The negative resist pattern is then removed and the unwanted copper is etched away. After etching, the conductor side-faces consist of bare copper.

#### 1.5.5 DIRECT METHOD

With the direct method an etching resist, usually of the photo sensitive variety, is applied over the conductor pattern. This method is used for boards without plated-through holes and without electroplating.

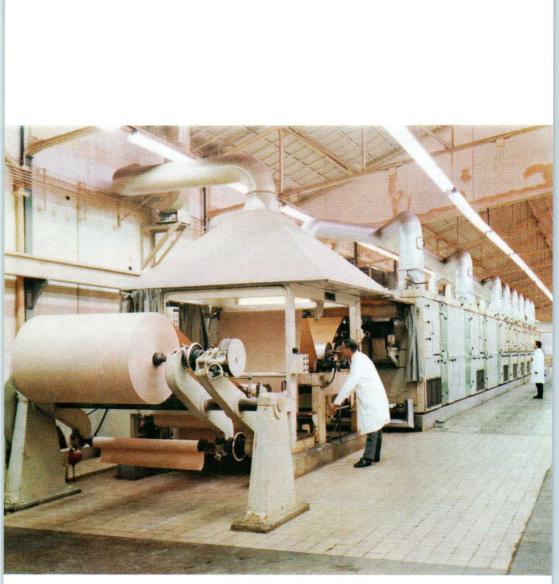

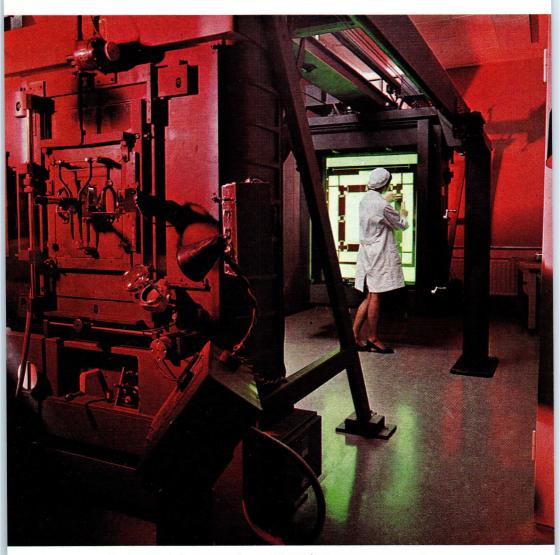

Manufacture of base material.

### 2 Base materials

#### 2.1 Classification

The most important base materials for PCB's fall into the following two main categories:

#### 2.1.1 PAPER BASE LAMINATES

These consist of paper layers impregnated with synthetic resin and laminated under heat and high pressure. Paper base phenolic resin and paper base epoxy resin laminates are commonly used. They are unsuitable as base material for boards with plated-through holes where the electrical interfacial connection (see Section 5) is important.

Where they are used, non-reproducible warp and twist must be taken into consideration.

As a rule, paper base laminates are not recommended for professional applications.

#### 2.1.2 GLASS BASE LAMINATES

These consist of glass-fabric or glass-fibre layers impregnated with synthetic resin and laminated under heat and high pressure. For PCB's with plated-through holes where the electrical interfacial connection is important, use is made of glass-fabric epoxy resin laminate and glass-fibre polyester resin laminate. Of the glass-fabric epoxy laminates the three most widely used grades are: FR-5 (flame retardant and temperature resistant); FR-4 (flame-retardant); and G-10 (general purpose). Of the glass-fibre polyester laminates the grade GC MIL-P13949D is preferred.

#### **2.2 Essential Properties**

#### 2.2.1 COMPARISON OF TYPES

The values quoted in Table 2.1 are for comparison only since they may vary from supplier to supplier.

| property                                               | paper base<br>phenol | paper base<br>epoxy | glass-fabric<br>base epoxy | glass-fibre<br>base<br>polyester |

|--------------------------------------------------------|----------------------|---------------------|----------------------------|----------------------------------|

| min. peel strength (N/mm)                              | 1.10                 | 1.25                | 1.25                       | 1.20                             |

| surface resistivity $(M\Omega^1)$                      | 10 <sup>3</sup>      | 10 <sup>3</sup>     | 104                        | 104                              |

| volume resistivity $(M\Omega^1)$                       | 104                  | 105                 | 106                        | 106                              |

| water absorption (%) dielectric constant $\varepsilon$ | 0.65                 | 0.55                | 0.35                       | 0.35                             |

| (f = 1 MHz)                                            | 5.3                  | 5                   | 5.8                        | 3.4                              |

| dissipation factor                                     |                      |                     |                            |                                  |

| $\tan \delta \times 10^{-4}$ (f = 1 MHz)               | 500                  | 450                 | 450                        | 115                              |

| min. flexural strength (N/cm <sup>2</sup> )            | 7000                 | 9000                | 31000                      | 20000                            |

| max. operating temp. (°C)<br>max. soldering time       | 110                  | 110                 | 125 <sup>2</sup> )         | 110                              |

| and temperature                                        | 5s /260 °C           | 15s /260 °C         | 30s /260 °C                | 10s /260 °C                      |

| price index                                            | 1                    | 2.5                 | 4                          | 1.5                              |

Table 2.1 Properties of base materials

<sup>1</sup>) Surface and volume resistance measured after 96 h at 35 °C and 90 % RH.

<sup>2</sup>) 125 °C for FR-4; 155 °C for FR-5, see 2.3.2

#### 2.2.2 SURFACE AND VOLUME RESISTANCE

When the PCB's have plated-through holes, certain requirements are made on the surface resistance (conductor pattern) as well as on the volume resistance (plated-through holes).

The resistance measured on the board is a combination of both the surface and the volume resistance, and is referred to simply as the insulation resistance.

The surface and volume resistances quoted in the base material specifications cannot be translated directly into an insulation resistance for the PCB. This is because the changes in the resistances are influenced in a non-linear manner according to the pattern dimensions (spacings). Hence, the insulation resistance can only be determined by measurements performed on the actual PCB.

A further consideration is that differences are found after long-term damp heat tests.

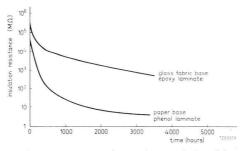

Fig. 2.1 shows the change in insulation resistance at 28  $^{\circ}$ C and 94  $^{\circ}_{0}$  RH measured on glass-fabric base epoxy and paper base phenol laminate PCB's of a given size. The difference in quality between the two laminates is evident.

Fig. 2.1. Change in insulation resistance of paper base and glass fabric laminate at  $28 \degree C$ and 94% RH.

The volume and surface resistance, as specified by the base material supplier, is determined by the "ring and disk" method given in IEC publication 249-1 (see para 9.3.5). In general, the volume resistance measured on plated-through holes at 0.1'' spacings will be less than this.

As a rule, the volume resistance of a PCB with plated-through holes must not change to a value of less than 100 M $\Omega$  during a humidity test.

#### 2.2.3 MAX. OPERATING TEMPERATURE

When PCB's, which have been subjected to a dip-soldering or wavesoldering operation, are used at the specified maximum operating temperature, a discoloration of the base material may occur. Hence, an operating temperature lower than the specified maximum operating temperature is recommended.

#### 2.2.4 FLATNESS LIMITS

The maximum warp or twist specified by the base material supplier relates to the base materials and not to the finished boards.

#### 2.3 Material Specification and U.L. Approval

#### 2.3.1 BASE MATERIALS

These are covered by the following specifications:

| MIL-P-139489      | paper base epoxy laminates and glass-fabric base lamina-<br>tes.               |

|-------------------|--------------------------------------------------------------------------------|

| NEMA LI-1         | paper base phenol, paper base expoxy, and glass-fabric base laminates.         |

| IEC-publ. 249-1   | test methods for metal clad base materials for printed circuits.               |

| IEC-publ. 249-2-1 | phenolic cellulose paper, high electrical quality.                             |

| IEC-publ. 249-2-2 | paper phenolic copper clad, economic grade.                                    |

| IEC-publ. 249-2-3 | epoxide cellulose copper clad laminated sheet, flame re-<br>tardant grade.     |

| IEC-publ. 249-2-4 | epoxide woven glass fabric copper clad laminated sheet, general purpose grade. |

| IEC-publ. 249-2-5 | epoxide woven glass fabric copper clad laminated sheet, flame retardant grade. |

The tests and the test methods quoted in the various specifications may differ, but the base materials which satisfy the various specifications are interchangeable.

The governing specifications are primarily the IEC publications. However, these have not yet been adopted by the suppliers of base materials and thus the base materials available on the market are covered by MIL and NEMA specifications.

For some properties the suppliers' specifications quote values which are higher than the minimum specifications quoted in the MIL and NEMA specifications.

#### 2.3.2 BASE MATERIALS IDENTIFICATION

Identification codes used in the various specifications are not standardised. The identifications for similar materials are given for comparison in Table 2.2.

| Туре                                                                       | NEMA  | MIL | IEC 249-2- |

|----------------------------------------------------------------------------|-------|-----|------------|

| phenol paper                                                               | хххр  | _   | PF-CP-Cu-1 |

| phenol paper, cold punching grade                                          | xxxpc |     | -          |

| epoxy paper, flame retardant                                               | FR-3  | PX  | EP-CP-Cu-3 |

| phenol paper, flame retardant                                              | FR-2  |     | -          |

| epoxy glass-fabric, general purpose                                        | G-10  | GE  | EP-GC-Cu-4 |

| epoxy glass-fabric, flame retardant<br>epoxy glass-fabric, flame retardant | FR-4  | GF  | EP-GC-Cu-5 |

| and temperature resistant                                                  | FR-5  | GH  | -          |

Table 2.2 Base material identification by code

Nearly all base materials of more than 0.8 mm thickness carry manufacturer's marks spaced at approximately 75 mm distance. The type of material is identified by the colour of the marks, see Table 2.3.

Table 2.3 Base material identification by colour

| type                                         | colour identification             |

|----------------------------------------------|-----------------------------------|

| glass-fabric, general purpose                | white                             |

| glass-fabric, flame retardant                | red                               |

| glass-fabric, temperature resistant          | black                             |

| paper base, all types except flame retardant | any contrasting colour except red |

| paper base, flame retardant                  | red                               |

#### 2.3.3 U.L. APPROVAL

The Underwriters' Laboratories Inc. approval for PCB's (see 9.4) may be obtained only if the base material has been given a U.L. file number.

The makes and types used by us and which have received U.L. approval are quoted in Table 2.4.

Table 2.4 U.L. Approved base materials

| manufacturer | type                          | U.L. file number   |

|--------------|-------------------------------|--------------------|

| mica-ply     | G10, FR4 and FR5              | E 39560            |

| mas.         | FR2, FR3, FR4, FR5<br>and G10 | E 41668 - 67M 2482 |

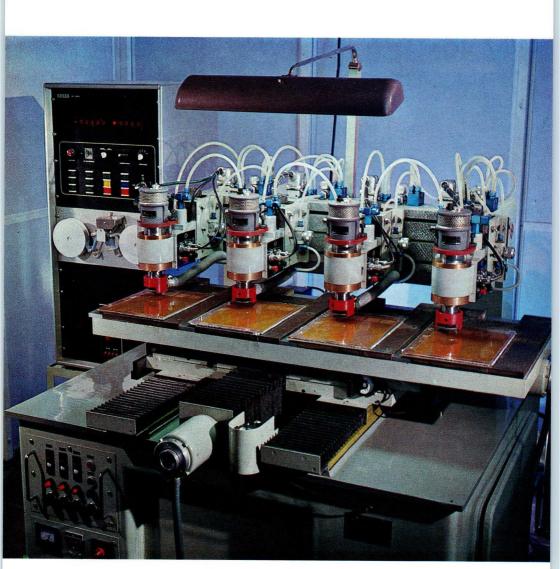

Four-spindle n.c. drilling machine.

## **3 Board Fabrication**

#### 3.1 Board Contour and its Location w.r.t. Holes and Pattern

The three board contouring methods employed are sawing, milling, and punching. The choice depends on the quantity of boards involved, the shape of the board and the tolerance. The punching method is preferred and is invariably used for long production runs. For short production runs of rectangular shaped boards, the sawing method is used. Any cut-outs which are required in the rectangular contour are then accomplished by milling.

For short production runs of non-rectangular shaped boards the milling method is used.

For short production runs of rectangular shaped boards, where the dimensions are not critical, the size may be judged by eye, printed sawing marks then serving as a guide.

Whether long or short run production, the board contour should be kept simple, i.e. rectangular with no cut-outs.

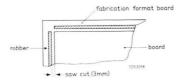

#### 3.1.1 CONTOURING BY SAWING WITH A SAWING JIG

This method employs a sawing jig centred on holes inside the board contour. The jig is moved past a straight-edge which is fixed with respect to the circular saw. The method is suitable for short production runs of rectangular boards.

Centring is accomplished by locating on three plated-through holes or, alternatively, two non-plated holes whose minimum diameter is 2 mm. The two non-plated holes provide the best anchorage and this method should always be used where awkward sized (very large, or very small) boards are being made.

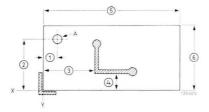

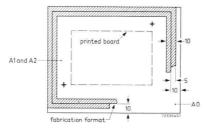

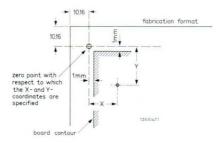

#### Dimensioning and tolerancing (Fig. 3.1)

- The sides X and Y are specified with respect to one hole "A", which may or may not be plated-through.

- The tolerance on the dimensions 1, 2, 5 and 6 is  $\pm$  0.2 mm.

- The pattern is automatically fixed with respect to the contour.

Fig. 3.1. Reference dimensions for rectangular PCB with no cut-outs.

- The dimensions 3 and 4 must not be entered (reference dimensions), they are shown here for information purposes only.

- The tolerance on the dimensions 3 and 4 depends on the pattern misalignment, which in turn depends on the pattern class.

- The tolerance is  $\pm 0.5\,$  mm for pattern class I.

$\pm$  0.33 mm for pattern class II and III.

- When the centring holes (A) are judged by eye, with printed centring areas serving as a guide, the tolerance on the dimensions 3 and 4 is  $\pm$  0.3 mm for all pattern classes.

#### 3.1.2 Contouring by milling

This method employs a milling jig which is centred on two holes inside the board contour. The jig is moved by hand past the non-cutting section of a vertical end mill. The method is suitable for short production runs of boards of any shape.

Centring is accomplished by locating on two non-plated holes whose minimum diameter is 2 mm.

#### Dimensioning and tolerancing

As 3.1.1

#### 3.1.3 CONTOURING BY SAWING WITHOUT A SAWING JIG

The board size is judged by eye, printed sawing marks serving as a guide. This method is suitable for short production runs of rectangular boards where the board dimensions are not critical.

#### Dimensioning and tolerancing (Fig. 3.1)

- Dimensioning is superfluous when the entire contouring operation consists of sawing to printed sawing marks.

- If two sides are cut by sawing to a stop, then the dimensions 5 and 6 have to be entered.

- When sawing to printed sawing marks only the tolerances are as follows:

Dimensions 1 and 2:  $\pm$  0.8 mm for pattern class I

$\pm$  0.6 mm for pattern class II and III

- 3 and 4:  $\pm$  0.5 mm, independent of pattern class.

- 5 and 6:  $\pm 1$  mm, independent of pattern class.

- When the sides X and Y are cut by sawing to printed sawing marks and the two opposite sides by sawing to a stop, the tolerance on the dimensions 5 and 6 is  $\pm$  0.2 mm.

#### 3.1.4 Contouring by punching

A die is used to cut the board to size in one or more operations. As the dies are expensive, this method is used only where the length of the production run justifies the cost. Two non-plated holes are used for centring.

Punching may be carried out at ambient temperature, or at a slightly higher temperature attained by preheating.

#### Dimensioning and tolerancing (Fig. 3.1)

- The sides X and Y are specified with respect to a plated-through hole.

- The tolerance on the dimensions 1, 2, 5 and 6 is  $\pm$  0.15 mm.

- The pattern is automatically fixed with respect to the contour.

- The dimensions 3 and 4 must not be entered (reference dimensions).

- The tolerance on the dimensions 3 and 4 depends on the pattern class.

- The tolerance is  $\pm$  0.5 mm for pattern class I

$\pm$  0.3 mm for pattern classes II and III

#### 3.1.5 Making cut-cuts by milling to a stop

Two sides are moved by hand past a stop which is adjustable with respect to a vertical end mill.

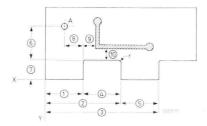

Fig. 3.2. Reference dimensions for PCB with cut-outs.

#### Dimensioning and tolerancing (Fig. 3.2)

- The dimensions are specified from the sides X and Y which serve as stops during the milling operation.

- Only the dimensions 1, 2, 3 and 7 are entered.

- The tolerance on the dimensions 1, 2, 3 and 7 is  $\pm$  0.1 mm.

- The corners should be provided with a radius of not less than 1.5  $\pm$  0.5.

- The dimensions 4, 5, 6, 8, 9 and 10 must not be entered (reference dimensions).

#### *Note 1* (board contouring to method 3.1.1)

The tolerance on the dimensions 6 and 8 is  $\pm$  0.3 mm and the tolerance on the dimensions 9 and 10 is  $\pm$  0.6 mm for pattern class I and  $\pm$  0.4 mm for pattern class II and III.

#### *Note 2* (board contouring to method 3.1.3)

The tolerance on the dimensions 6 and 8 is  $\pm$  0.9 mm for pattern class I and  $\pm$  0.7 mm for pattern class II and III; the tolerance on the dimensions 9 and 10 is  $\pm$  0.6 mm irrespective of the pattern class.

#### 3.1.6 MILLING CUT-OUTS BY MEANS OF A MILLING JIG

As mentioned in para 3.1.2, with the cut-outs being part of the contour.

#### Dimensioning and tolerancing (Fig. 3.2)

- The dimensions 1, 3, 4 and 7 are entered.

- The tolerance on these dimensions is  $\pm$  0.2 mm.

- The dimensions 6, 8, 9 and 10 are not entered (reference dimensions)

- The tolerance on the dimensions 6 and 8 is  $\pm$  0.2 mm.

- The tolerance on the dimensions 9 and 10 is  $\pm$  0.3 mm for all pattern classes.

- With this method, centring holes with respect to pattern have to be made by eye, with printed centring areas serving as a guide.

#### 3.2 Hole Size

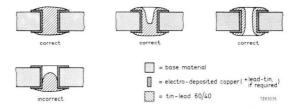

#### 3.2.1 Plated-through holes

The plated-through hole diameter must satisfy the following requirement: Nominal hole diameter in whole tenths of millimeters =

$\geq \frac{\text{nominal board thickness}}{3}$

Preferred diameters are:  $0.6 (\pm 0.1)$ ,  $0.8 (\pm 0.1)$ ,  $1 (\pm 0.13)$ ,  $1.3 (\pm 0.13)$  mm. Interfacial connection in double-sided PCB's up to 1.6 mm in thickness may be made via a plated-through hole of 0.5 (-0.2) mm diameter. That is if the plated-through hole is not to be used for component mounting.

#### 3.2.2 NON-PLATED HOLES

Drilled plain holes of any diameter are available in whole tenths of millimeters.

The tolerance on the diameter is:

- $\pm$  0.05 mm when diameter is  $\leq$  0.8 mm

- $\pm$  0.1 mm when diameter is  $\leq$  0.9 mm.

In the case of punched holes, the diameter and tolerance depend on the die used, but in general the tolerance on the diameter will be  $\pm$  0.1 mm. The diameter must not be less than:

nominal board thickness

2

Forty-spindle automatic jig drilling machine (foreground).

#### 3.3 Tolerance on Hole Spacing

#### 3.3.1 Plated-through holes

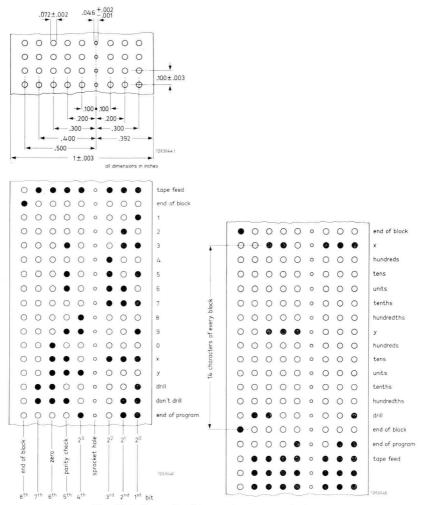

These holes are drilled with a numerically controlled drilling machine programmed with information on hole location via a punched tape. In principle the tape information may be derived from one of three sources:

- I The master pattern.

- II A list of co-ordinates.

- III Direct from a tape used to programme a numerically controlled drawing machine for artwork generation.

#### Method I

- The drilled holes have a radial deviation of max. 0.08 mm with respect to the location on the master pattern.

- The tolerance on the hole spacing is  $2 \times 0.08 = \pm 0.16$  mm with respect to the master pattern.

- The hole spacing of the finished board is guaranteed with respect to the spacing on the master pattern.

- When the spacing is more than 200 mm, a larger tolerance must be taken into consideration. This is due to expansion or shrinkage during the PCB fabrication process (see para 3.4.1).

- No requirements can be made on the nominal hole spacing since this depends on the accuracy of the artwork, the master pattern and the punched tape information.

This undefined hole spacing may present difficulties when components are mounted on the printed board by automatic methods.

- As the hole and pattern locations are derived from the same master, the pattern to hole registration is good.

#### Method II

- When the pattern is not made on a numerically controlled drawing machine, the hole location is determined independently from the pattern. The pattern to hole registration is then determined by the accuracy achieved in the artwork.

- In practice, artwork not made by an automatic method does not possess sufficient accuracy of hole to terminal-area registration and therefore this method cannot be adopted.

#### Method III

- This method is preferred since the hole and the pattern locations are determined from the same coordinates.

- The drilled holes have a radial deviation of max. 0.05 mm with respect to the master pattern.

- The tolerance on the hole spacing is  $2\times 0.05=\pm 0.1$  mm with respect to the master pattern.

- The hole spacing of the finished board is guaranteed with respect to the spacing on the master pattern.

- When the hole spacing is more than 200 mm, a tolerance increase must be taken into consideration. This is due to expansion or shrinkage during the PCB fabrication process (see para 3.4.1).

- This method permits the highest possible accuracy as far as the registration of the pattern, holes, and hole spacing is concerned.

- It is the obvious method to employ when automated component mounting techniques are in use.

#### 3.3.2 Non-plated holes

Three methods are available for obtaining non-plated holes. They are always made after PCB fabrication has been completed, unless the dry film resist "tenting over" technique is used.

#### Method I Reaming a plated-through hole

- A pre-requisite is that the plain hole is at least 0.5 mm larger than the plated-through hole and that it is indicated on the master pattern, or on the tape for the numerically controlled drilling machine.

- Reamed holes have a radial deviation of 0.1 mm with respect to the location on the master pattern.

- The tolerance on the hole spacing is  $2 \times 0.1 = \pm 0.2$  mm when method 3.3.1 (I) is used, and the radial deviation is 0.075 mm (tolerance on the hole spacing is  $2 \times 0.075 = \pm 0.15$  mm) when the plated-through holes are made by method 3.3.1 (II)

- When the hole spacing is more than 200 mm, a tolerance increase must be taken into consideration. This is due to expansion or shrinkage of the base material during the PCB fabrication process (see para 3.4.1).

#### Method II Drilling by means of the numerically controlled drilling machine

- Holes of diameter up to 4 mm, may be made by means of the numerically controlled drilling machine.

- The tolerance on the location of these holes is as in method 3.3.1 (III).

- A separate tape has to be made to provide hole location information in terms of the coordinates.

#### Method III Using a drilling jig

- Tolerance on hole spacing is:

- $\pm$  0.05 mm when spacing is  $\leq$  200 mm

- $\pm$  0.1 mm when spacing is > 200 mm

- The drilling jig may be centred with respect to the board edge.

- The tolerance on the hole location with respect to the board edge is  $\pm$  0.1 mm.

# 3.4 Dimensional Changes Caused by Shrinkage and/or Expansion of the Base Material

The characteristics of the base material influence the ultimate board size in two ways:

# 3.4.1 Permanent dimensional changes caused by the PCB fabrication process

This should be taken into account when determining the hole spacing for the master pattern or tape for the drilling machine. It relates to holes made at the start of the PCB fabrication process, i.e. plated-through holes; and plain holes made by reaming plated-through holes. These are subject to the cumulative effects of the entire fabrication process. When the hole spacing is more than 200 mm, an extra deviation must be taken into consideration (see also sub-section 3.3). This is + 0.05% for glass fabric and -0.125% for paper base phenol.

Mechanical operations carried out after the completion of the fabrication process do not require a dimensional change allowance.

#### 3.4.2 DIMENSIONAL CHANGES IN THE FINISHED BOARD DUE TO TEMPERATURE

The specified coefficient of linear expansion enables the dimensional change to be calculated, but the change occurring in practice may deviate from the calculated change. This is because the coefficients of expansion may vary according to supplier and the change with temperature is not always linear.

The approximate figures are  $1.5\times10^{-5}/^\circ C$  for glass fabric,  $1.7\times10^{-5}/^\circ C$  for paper base phenol and  $2.5\times10^{-5}/^\circ C$  for paper base epoxy.

# **3.5 Flatness Limits**

In the board fabrication process the flatness of the base material which is specified on the applicable material standard (see para 2.2.4), is influenced in a non-reproducible way by the shape and distribution of the pattern. Flatness limits specified on the board drawing, may never be better than those quoted for the base material.

As flatness is a hardly reproducible variable on which the board manufacturer has little or no control, its specification on the board drawing usually implies an extra high reject percentage due to the boards being outside the specified limit. Thus it is always advisable to take a certain warpage into consideration when designing the device in which the board is to be housed.

#### 3.5.1 Specifying flatness

Any departure of the board from being a flat surface has previously been specified in terms of "warp" and "twist". In view of the difficulty of defining what precisely constitutes "warp" as distinct from "twist", a recent IEC publication proposes that the future criterion be "flatness".

The proposed means of specifying a maximum permissible deviation from flatness is by reference to a specified maximum radius of curvature of the PCB diagonal. This is described in sub-section A5.2.

# 4 Pattern

# 4.1 General

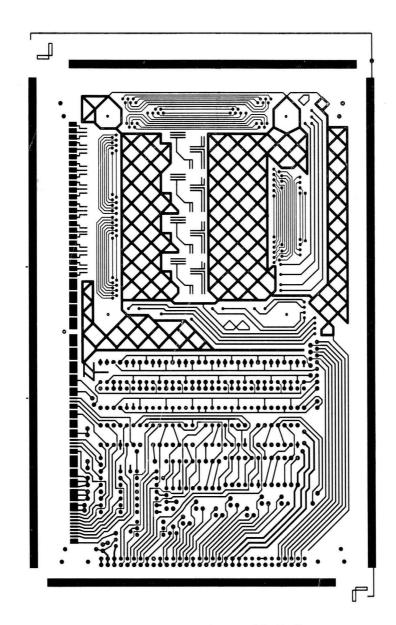

A master pattern will always be required whatever the fabrication process may be. It is a precision photo reduction derived from a large scale artwork. Details on the production of artwork are given in Section 10.

Depending upon which fabrication process is adopted, the finished PCB will exhibit certain deviations from the master pattern. The width of the conductors and the diameter of the terminal areas will differ from those on the master pattern. The conductor edges may exhibit blemishes and the pattern as a whole will exhibit a certain misalignment with respect to the holes. Allowance has therefore to be made on the artwork to accommodate these deviations. Since they will be dependent on the fabrication process, separate artworks will be required if the same pattern is to be used with different processes.

The maximum allowable process-dependent deviations are quoted in the Appendix, Table A2. The dimensions of the finished PCB are guaranteed to be within the specified maximum allowable deviations, but only with respect to the master pattern.

# 4.2 Pattern Classes

The specifications given in the Appendix refer to "Board classes". Each class represents a degree of processing difficulty resulting from a combination of board size and pattern detail. Obviously, the larger the board and the finer the pattern, the greater will be the effects of tolerances and the difficulties of inspection.

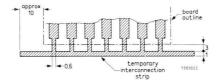

The Appendix lists a number of board sizes (Table A1) and a number of pattern classes (Table A2) and also indicates their possible combinations to form board classes. The board sizes quoted in Table A2 are nett sizes which are mandatory maxima in a given board class. In principle there are no limitations on size. As soon as a board size appertaining to a board class is exceeded, the next board class will become applicable and the maximum board size will be the size appertaining to that class. Small sizes may be combined into a large size and in that case an edge of at least 5.08 mm (2e) has to be left around each of the small sizes, i.e. a spacing of 4e between the board outlines. When the desired conductor width and spacing are minimum values, the most critical feature of a pattern class, as quoted in Table A2, is the conductor pitch, since the closer the tolerances in a given process, the smaller the conductor pitch will be. Table A2 also quotes a minimum conductor pitch for each class, it being assumed that the conductor width and spacing of the finished PCB are also minimum values.

A pattern may combine several pattern classes. In that case the board class is based on the distribution and number of the most difficult pattern classes occurring in the pattern. Wherever possible, the conductors and conductor spacing should be made wide and the terminal areas large. Difficult pattern classes should be avoided, except where absolutely necessary. The Appendix includes graphs to show how the limits can be found for dimensions of the finished board from the corresponding master pattern dimensions. A method of determining the artwork dimensions from the specified minimum conductor width and spacing of the finished PCB follows in sub-section 4.5.

# 4.3 Pattern Tolerances

To determine the pattern tolerance (i.e. the limits within which the pattern of the finished PCB may deviate from the design dimensions) two types of deviation must be identified. First, the deviations which occur in the artwork and the master pattern (master pattern tolerance) and second, deviations which occur when the PCB is made (fabrication tolerance).

#### 4.3.1 MASTER PATTERN TOLERANCE

This tolerance defines the limits within which the dimensions and locations of conductors and terminal areas, as measured on the master pattern, may deviate from the corresponding design figures. The tolerance is necessary to allow for the accumulated deviations occurring when the artwork and master pattern are made. The maximum permissible master pattern tolerances are specified for each pattern class in Table A2.

#### 4.3.2 FABRICATION TOLERANCE

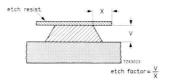

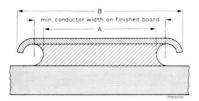

This defines the limits within which the pattern of the finished PCB may deviate from the master pattern. It relates to conductor width and terminal area diameter and to blemishes in the pattern edges.

# Fabrication tolerance on conductor width and terminal area diameter

This defines the limits within which the width of conductors and the diameter of terminal areas may deviate from the corresponding width and diameter measured on the master pattern. It allows for deviations occurring when the resist pattern is applied and for possible overhang of the plating.

The tolerance depends on the processing method and is given for each pattern class in Table A2.

#### Blemishes along the edges of the conductor pattern

According to the adopted processing method, blemishes occur to a greater or lesser degree along the edges of the conductor pattern. They can be isolated projections (excess metal) or isolated indentations or voids (missing metal). Any excess metal reduces the conductor spacing and missing metal reduces the conductor width. These blemishes have to be accounted for in the artwork.

The maximum permissible excess metal is expressed as a percentage of the minimum conductor spacing of the finished board and the maximum permissible missing metal is expressed as a percentage of the minimum conductor width of the finished board. Both are specified in Table A2 on page 106 for each processing method and each pattern class.

# 4.4 Misalignment of Pattern with Respect to Holes

The misalignment is not measured directly. It is derived by measuring the smallest distance from the hole edge to the terminal area edge on the finished PCB. The *minimum* permissible distance is specified in Table A2. The misalignment of the pattern varies according to the processing method. The minimum alignment tolerance needed in the pattern fabrication process by a given method, is specified in Table A2.

The minimum misalignment of the finished PCB pattern needed in the fabrication process is defined as follows: it is the distance by which a minimum diameter terminal area may be out of position, with respect to a maximum diameter non-plated or plated-through hole, which still provides that the permissible minimum distance from hole edge to terminal area edge is not violated. The minimum permissible terminal area diameters which are in accordance with the above, are specified per pattern class in Table A2. These diameters are nominal artwork dimensions on 1 to 1 scale. It is recommended that the largest possible terminal area diameter should be used. The larger the board, the larger the terminal area diameter should be.

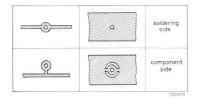

| configuration | average          | screen resist to para 1.5.1. |            |           |               |                     |                   | - 6                  |

|---------------|------------------|------------------------------|------------|-----------|---------------|---------------------|-------------------|----------------------|

|               | hole<br>diameter | mini<br>A                    | mum p<br>B | itch<br>D | pitch in<br>A | inches<br>B         | D                 | for-<br>mat          |

|               | $0.6\pm0.1$      | 1.66                         | —          | 1.2       | 1.9053(4e)    |                     | 1.4               | $\leq 2$             |

|               | $0.8\pm0.1$      | 1.86                         | -          | 1.4       | 1.9053(4e)    |                     | 1.4               | >2<br>$\leq 2$<br>>2 |

|               | $1\pm0.13$       | 2.06                         | —          | 1.6       | 2.54(1e)      | _                   | 2                 | $\leq 2$             |

|               | $1.3\pm0.13$     | 2.36                         | _          | 1.9       | 2.54(1e)      | _                   | 2                 | >2<br>$\leq 2$<br>>2 |

|               | 0.6 ± 0.1        | 2.33                         | 0.25       | 1.2       | 2.54(1e)      | 0.35                | 1.2               | $\leq 2$             |

|               | $0.8\pm0.1$      | 2.53                         | 0.25       | 1.4       | 2.54(1e)      | 0.25<br>0.25        | 1.4<br>1.4        |                      |

|               | $1\pm0.13$       | 2.73                         | 0.25       | 1.6       | 3.1755(4e)    | 0.35<br>0.3         | 1.8<br>1.9        |                      |

| Ŵ             | $1.3\pm0.13$     | 3.03                         | 0.25       | 1.9       | 3.1755(4e)    | 0.35<br>0.25        | 1.9<br>2          | $\leq 2$<br>> 2      |

|               | 0.6 ± 0.1        | 3                            | 0.25       | 1.2       | 3.1755(4e)    | 0.3                 | 1.2               | $\leq 2$             |

|               | $0.8\pm0.1$      | 3.2                          | 0.25       | 1.4       | 3.811(5e)     | 0.25                | 1.3<br>1.4        |                      |

|               | $1\pm0.13$       | 3.4                          | 0.25       | 1.6       | 3.811(5e)     | 0.3<br>0.35<br>0.3  | 1.6<br>1.6<br>1.9 |                      |

|               | $1.3\pm0.13$     | 3.7                          | 0.25       | 1.9       | 3.811(5e)     | 0.25<br>0.25        | 1.9<br>1.9<br>2   |                      |

|               | 0.6 ± 0.1        | 3.7                          | 0.25       | 1.2       | 3.811(5e)     | 0.25                | 1.2               |                      |

|               | $0.8\pm0.1$      | 3.9                          | 0.25       | 1.4       | 4.457(4e)     | 0.25<br>0.4<br>0.3  | 1.3<br>1.4<br>1.6 |                      |

|               | $1\pm0.13$       | 4.1                          | 0.25       | 1.6       | 4.457(4e)     | 0.3<br>0.35<br>0.3  | 1.6<br>1.8        |                      |

|               | $1.3\pm0.13$     | 4.4                          | 0.25       | 1.9       | 4.457(4e)     | 0.3<br>0.25<br>0.25 | 1.8<br>1.9<br>1.9 |                      |

|               |                  | 0.675                        | 0.25       |           | 0.76(30 mil)  | 0.3                 | _                 |                      |

Table 4.1 Nominal artwork dimensions

|                                                                                               | average .        |           | dr          | y film : | resist to para 1 | .5.2               |                   |                                                      |

|-----------------------------------------------------------------------------------------------|------------------|-----------|-------------|----------|------------------|--------------------|-------------------|------------------------------------------------------|

| configuration                                                                                 | hole<br>diameter | mini<br>A | mum pi<br>B | tch<br>D | pitch ir<br>A    | n inches<br>B      | D                 | for-<br>mat                                          |

|                                                                                               | $0.6\pm0.1$      | 1.47      |             | 1.2      | 1.9053(4e)       |                    | 1.4<br>1.6        | $\leq 2$<br>> 2                                      |

|                                                                                               | $0.8 \pm 0.1$    | 1.67      |             | 1.4      | 1.9053(4e)       |                    | 1.5<br>1.6        | $  \geq 2$<br>$\leq 2$<br>> 2                        |

|                                                                                               | $1\pm0.13$       | 1.87      |             | 1.6      | 1.9053(4e)       |                    | 1.6<br>1.6        | $\leq 2$<br>$\leq 2$<br>> 2                          |

| · 🏈 📑                                                                                         | $1.3\pm0.13$     | 2.17      | _           | 1.9      | 2.54(1e)         |                    | 2<br>2.2          | $\leq 2$<br>$\geq 2$<br>> 2                          |

|                                                                                               | 0.6 ± 0.1        | 1.97      | 0.25        | 1.2      | 2.54)1e)         | 0.35               | 1.4<br>1.5        | $\leq 2$<br>> 2                                      |

|                                                                                               | $0.8\pm0.1$      | 2.17      | 0.25        | 1.4      | 2.54(1e)         | 0.3<br>0.35<br>0.3 | 1.5<br>1.5<br>1.6 | $  \geq 2$<br>$\leq 2$<br>> 2                        |

|                                                                                               | $1\pm0.13$       | 2.37      | 0.25        | 1.6      | 2.54(1e)         | 0.3                | 1.6               | $  \geq 2$<br>$\leq 2$<br>> 2                        |

| - <del>@</del>                                                                                | $1.3\pm0.13$     | 2.67      | 0.25        | 1.9      | 3.1755(4e)       | 0.4<br>0.3         | 1.9<br>2.2        | $\leq 2$<br>$\leq 2$<br>> 2                          |

|                                                                                               | $0.6\pm0.1$      | 2.47      | 0.25        | 1.2      | 2.54(1e)         | 0.25               | 1.2               | $\leq 2$<br>> 2                                      |

|                                                                                               | $0.8\pm0.1$      | 2.67      | 0.25        | 1.4      | 3·1755(4e)       | 0.35<br>0.3        | 1.4<br>1.6        | $\begin{vmatrix} > 2 \\ \leq 2 \\ > 2 \end{vmatrix}$ |

|                                                                                               | $1\pm0.13$       | 2.87      | 0.25        | 1.6      | 3.1755(4e)       | 0.3                | 1.6               | $  \geq 2$<br>$\leq 2$<br>> 2                        |

|                                                                                               | $1.3\pm0.13$     | 3.17      | 0.25        | 1.9      | 3.1755(4e)       | 0.25               | 1.9               | $  \geq 2$<br>$\leq 2$<br>> 2                        |

|                                                                                               | 0.6 ± 0.1        | 2.97      | 0.25        | 1.2      | 3.1755(4e)       | 0.3                | 1.2               | $\leq 2$<br>> 2                                      |

|                                                                                               | $0.8\pm0.1$      | 3.17      | 0.25        | 1.4      | 3.1755(4e)       | 0.25               | 1.4               | > 2<br>$\leq 2$<br>> 2                               |

|                                                                                               | $1\pm0.13$       | 3.37      | 0.25        | 1.6      | 3.811(5e)        | 0.35<br>0.25       | 1.6<br>1.8        | $  \geq 2$<br>$\leq 2$<br>> 2                        |

|                                                                                               | $1.3\pm0.13$     | 3.67      | 0.25        | 1.9      | 3.811(5e)        | 0.25               | 1.9               | $\leq 2$<br>$\geq 2$<br>> 2                          |

| B                                                                                             |                  | 0.508     | 3 0.25      |          | 0.508(20 mi      | 1) 0.25            | _                 | $\leq 2$<br>> 2                                      |

| master pattern tolerance on width: $\pm$ 0.02, on pitch: $\pm$ 0.02<br>top-bottom: $\pm$ 0.03 |                  |           |             |          |                  |                    |                   |                                                      |

## 4.5 Establishing Artwork Dimensions

In order to establish the dimensions, the pattern class (see para 4.2) has to be known. If the pattern class is not known, the procedure is started on the basis of the least fine class and if the available space is found to be insufficient, a finer class is adopted. The calculated dimensions for the artwork have to be multiplied by an enlargement factor, as, where possible, the artwork should be prepared on the largest possible scale.

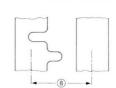

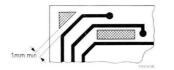

#### 4.6 Minimum Pattern Configuration

Table 4.1 shows various configurations and the required minimum pitch, minimum conductor width and minimum terminal area diameter. All dimensions quoted in Table 4.1 are nominal artwork dimensions based on the minimum finished PCB conductor width and spacing being not less than 0.2 mm. The nearest raster dimension is given for each minimum spacing (1e = 2.54 mm). These raster dimensions are, in general, larger than the minimum possible pitch. The difference is distributed over the conductor width, conductor spacing, and terminal area diameter, in a manner which is favourable from a printing point of view according to PCB size (see sub-section A 2.1).

The dimensions are calculated according to the sequence below. The relevant tolerances are specified in Table A2, together with the percentages of "missing" or "excess" metal.

Minimum conductor width on finished PCB in places where there are indentations and when width on master pattern is at its minimum. This is a "given" value decided by arrangement between customer and supplier.

Minimum conductor width on finished PCB when width on master pattern is at its minimum. This is calculated from the maximum permissible percentage of "missing"

metal.  $2 = \frac{100}{100 - \% \text{ missing metal}} \times I$

3. Nominal conductor width on finished PCB when width on master pattern is at its minimum. Calculated from the minus tolerance on the conductor width. 3 = 2 + (minus tolerance on conductor width) +3+

- 4. Nominal conductor width on artwork. Calculated from the minus master pattern tolerance.

4 = 3 + (minus master pattern tolerance on conductor width)

- 5. Maximum conductor width on finished PCB. Calculated from the plus tolerance on conductor width and the plus tolerance on master pattern.

- 5 = 4 + (plus tolerance on conductor width) + (plus master pattern tolerance).

*Remark:* Minimum conductor width may be adhered to as in point *I*.

Percentage missing metal is then greater than in point 2.

- 6. Minimum conductor spacing on finished PCB in places where there is excess metal. This is a "given" value which is decided by arrangement between customer and supplier. (It is the smallest conductor spacing permissible in places on a finished PCB.

- 7. Minimum conductor spacing on finished PCB where there is no excess metal at pattern edge.

Calculated from the permissible percent of excess metal

$$7 = \frac{100}{100 - \% \text{ excess metal}} \times 6$$

When no excess metal is permitted, 7 = 6.

8. Minimum conductor pitch on finished PCB

8 = 5 + 7.

9. Nominal conductor pitch on artwork. Calculated from the minus master pattern tolerance on pitch.

9 = 8 + (minus master pattern tolerance on pitch)

-) (6)

10. Terminal area diameter on artwork.

10 = terminal area diameter as specified in Table A2. If this diameter has to be calculated:

$$\label{eq:max} \begin{split} \mathit{l0} = d_{max} + 2M + t_p + t_f + 2L + 2V \\ \text{where} \end{split}$$

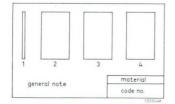

$d_{max} = max$ . diameter of plated-through hole